Journal Description

Chips

Chips

is an international, peer-reviewed, open access journal on all aspects of chips published quarterly online by MDPI.

- Open Access— free for readers, with article processing charges (APC) paid by authors or their institutions.

- Rapid Publication: first decisions in 16 days; acceptance to publication in 5.8 days (median values for MDPI journals in the second half of 2023).

- Recognition of Reviewers: APC discount vouchers, optional signed peer review and reviewer names are published annually in the journal.

- Companion journal: Sensors.

Latest Articles

Slew-Rate Enhancement Techniques for Switched-Capacitors Fast-Settling Amplifiers: A Review

Chips 2024, 3(2), 98-128; https://0-doi-org.brum.beds.ac.uk/10.3390/chips3020005 - 17 Apr 2024

Abstract

►

Show Figures

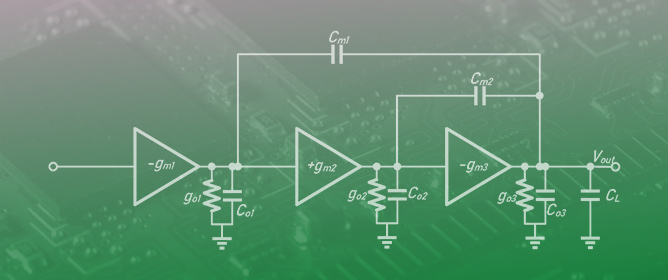

This review is aimed at the integrated circuit design community and it explores slew-rate enhancement techniques for switched-capacitor amplifiers, with a primary focus on optimizing settling time within power constraints. Key challenges are addressed, including the selection between single-stage and two-stage amplifiers, along

[...] Read more.

This review is aimed at the integrated circuit design community and it explores slew-rate enhancement techniques for switched-capacitor amplifiers, with a primary focus on optimizing settling time within power constraints. Key challenges are addressed, including the selection between single-stage and two-stage amplifiers, along with the utilization of advanced circuit-level techniques for slew-rate enhancement. Presently, there exists a gap in comprehensive discussion, with reliance primarily on two Figures of Merit aimed at assessing power efficiency under specific capacitive loads. However, these metrics fail to adequately assess the performance of the existing slew-rate enhancer solutions at different values of capacitive loads. As a consequence, the designer lacks clear guidelines in practical situations. This review provides a state-of-the art mapping under a figure of merit dedicated to assess the whole settling delay, and also introduces a novel performance metric which highlights the role of the circuital architectures, regardless of external operating conditions. By offering a thorough examination, this review seeks to steer future research in switched-capacitor amplifier design, thereby facilitating informed decision-making and fostering innovation in the field.

Full article

Open AccessArticle

Using the LabVIEW Simulation Program to Design and Determine the Characteristics of Amplifiers

by

Corina Cuntan, Caius Panoiu, Manuela Panoiu, Ioan Baciu and Sergiu Mezinescu

Chips 2024, 3(2), 69-97; https://0-doi-org.brum.beds.ac.uk/10.3390/chips3020004 - 01 Apr 2024

Abstract

►▼

Show Figures

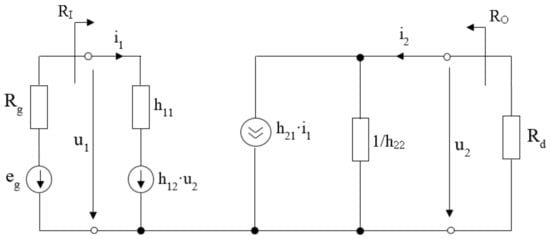

Because of the large number of parameters that interact in amplifier functions, determining dynamic regime parameters as well as the mode of function of amplifier stages is an extremely complex problem. This paper describes a LabVIEW application for studying the functioning of an

[...] Read more.

Because of the large number of parameters that interact in amplifier functions, determining dynamic regime parameters as well as the mode of function of amplifier stages is an extremely complex problem. This paper describes a LabVIEW application for studying the functioning of an amplifier in various connections. The user selects the generator’s parameters, the type of connection and its parameters, as well as the load circuit characteristics. The application can determine both the stage characteristics and the Bode characteristics. The amplifier’s stability zone, as well as its gain and phase, are determined based on these characteristics. An important advantage of this application is that the design of the amplifier stage can be created starting from some parameters that the amplifier can establish, from which the values of components can be determined. In order to validate the simulation results from the LabVIEW application, the specialized program Multisim was used, as well as experimental measurements using the Electronics Explorer Board. Both Multisim and Electronics Explorer Board can determine Bode characteristics. In both simulations and experimental amplifiers, the same schemes with the same transistor were used. The application can be used for educational purposes as well as to design an amplifier’s stage to achieve specific parameters.

Full article

Figure 1

Open AccessArticle

High-Efficiency Reconfigurable CMOS RF-to-DC Converter System for Ultra-Low-Power Wireless Sensor Nodes with Efficient MPPT Circuitry

by

Roberto La Rosa, Danilo Demarchi, Sandro Carrara and Catherine Dehollain

Chips 2024, 3(1), 49-68; https://0-doi-org.brum.beds.ac.uk/10.3390/chips3010003 - 12 Mar 2024

Abstract

►▼

Show Figures

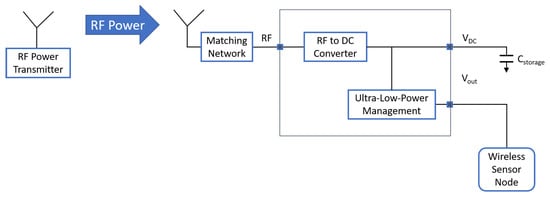

This paper presents a novel CMOS RF-to-DC converter for ultra-low-power wireless sensor nodes powered by RF wireless power transfer. The proposed converter achieves 10% higher power conversion efficiency than a conventional rectifier, with only a 1% increase in power consumption. The system employs

[...] Read more.

This paper presents a novel CMOS RF-to-DC converter for ultra-low-power wireless sensor nodes powered by RF wireless power transfer. The proposed converter achieves 10% higher power conversion efficiency than a conventional rectifier, with only a 1% increase in power consumption. The system employs a reconfigurable Dickson topology, operates on the unlicensed 868 MHz ISM band, and includes a built-in power-efficient MPPT system architecture. Experimental measurements show a maximum power conversion efficiency of 55% in the power range from −22 dBm to 0 dBm, with a power sensitivity of −22 dBm for a DC output voltage of 2.4 V. The proposed converter offers a promising solution for efficient wireless power transfer and energy harvesting in ultra-low-power wireless sensor nodes.

Full article

Figure 1

Open AccessArticle

Real-Time Compact Digital Processing Chain for the Detection and Sorting of Neural Spikes from Implanted Microelectrode Arrays

by

Andrea Vittimberga, Riccardo Corelli and Giuseppe Scotti

Chips 2024, 3(1), 32-48; https://0-doi-org.brum.beds.ac.uk/10.3390/chips3010002 - 08 Feb 2024

Abstract

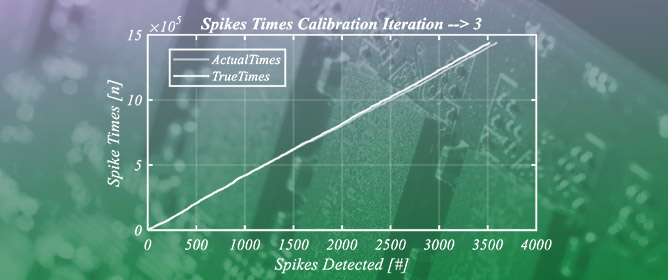

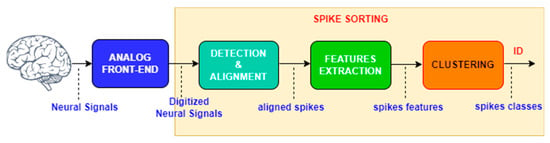

Implantable microelectrodes arrays are used to record electrical signals from surrounding neurons and have led to incredible improvements in modern neuroscience research. Digital signals resulting from conditioning and the analog-to-digital conversion of neural spikes captured by microelectrodes arrays have to be elaborated in

[...] Read more.

Implantable microelectrodes arrays are used to record electrical signals from surrounding neurons and have led to incredible improvements in modern neuroscience research. Digital signals resulting from conditioning and the analog-to-digital conversion of neural spikes captured by microelectrodes arrays have to be elaborated in a dedicated DSP core devoted to a real-time spike-sorting process for the classification phase based on the source neurons from which they were emitted. On-chip spike-sorting is also essential to achieve enough data reduction to allow for wireless transmission within the power constraints imposed on implantable devices. The design of such integrated circuits must meet stringent constraints related to ultra-low power density and the minimum silicon area, as well as several application requirements. The aim of this work is to present real-time hardware architecture able to perform all the spike-sorting tasks on chip while satisfying the aforementioned stringent requirements related to this type of application. The proposed solution has been coded in VHDL language and simulated in the Cadence Xcelium tool to verify the functional behavior of the digital processing chain. Then, a synthesis and place and route flow has been carried out to implement the proposed architecture in both a 130 nm and a FD-SOI 28 nm CMOS process, with a 200 MHz clock frequency target. Post-layout simulations in the Cadence Xcelium tool confirmed the proper operation up to a 200 MHz clock frequency. The area occupation and power consumption of the proposed detection and clustering module are 0.2659 mm2/ch, 7.16 μW/ch, 0.0168 mm2/ch, and 0.47 μW/ch for the 130 nm and 28 nm implementation, respectively.

Full article

(This article belongs to the Topic Applied System on Biomedical Engineering, Healthcare and Sustainability 2023)

►▼

Show Figures

Figure 1

Open AccessArticle

A 0.5-V Four-Stage Amplifier Using Cross-Feedforward Positive Feedback Frequency Compensation

by

Feifan Gao and Pak Kwong Chan

Chips 2024, 3(1), 1-31; https://0-doi-org.brum.beds.ac.uk/10.3390/chips3010001 - 30 Dec 2023

Abstract

►▼

Show Figures

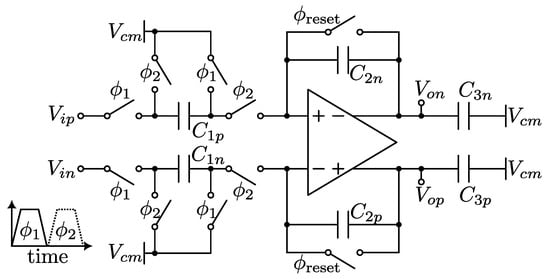

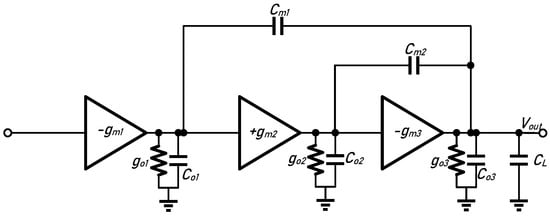

This paper presents a low-voltage CMOS four-stage amplifier operating in the subthreshold region. The first design technique includes the cross-feedforward positive feedback frequency compensation (CFPFC) for obtaining better bandwidth efficiency in a low-voltage multi-stage amplifier. The second design technique incorporates both the bulk-drain-driven

[...] Read more.

This paper presents a low-voltage CMOS four-stage amplifier operating in the subthreshold region. The first design technique includes the cross-feedforward positive feedback frequency compensation (CFPFC) for obtaining better bandwidth efficiency in a low-voltage multi-stage amplifier. The second design technique incorporates both the bulk-drain-driven input stage topology in conjunction with a low-voltage attenuator to permit operation at a low voltage, and improves the input common-mode range (ICMR). The proposed circuit is implemented using TSMC-40 nm process technology. It consumes 0.866 μW at a supply voltage of 0.5 V. With a capacitive load of 50 pF, this four-stage amplifier can achieve 84.59 dB in gain, 161.00 kHz in unity-gain bandwidth, 96 deg in phase margin, and 5.7 dB in gain margin whilst offering an input-referred noise of 213.63

Figure 1

Open AccessReview

Winner-Take-All and Loser-Take-All Circuits: Architectures, Applications and Analytical Comparison

by

Ehsan Rahiminejad and Hamed Aminzadeh

Chips 2023, 2(4), 262-278; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2040016 - 08 Nov 2023

Abstract

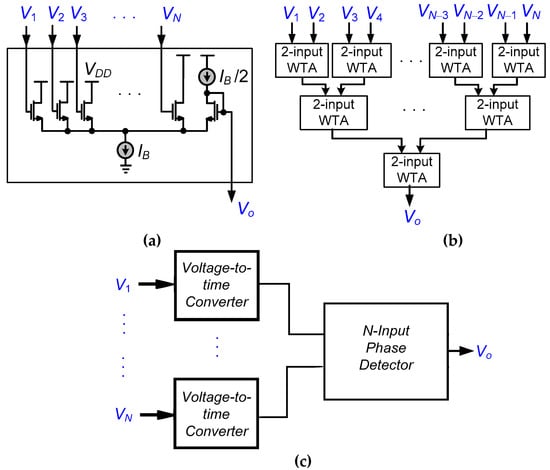

Different winner-take-all (WTA) and loser-take-all (LTA) circuits are studied, and their operations are analyzed in this review. The exclusive operation of the current conveyor, binary tree, and time-domain WTA/LTA architectures, as the most important architectures reported in the literature, are compared from the

[...] Read more.

Different winner-take-all (WTA) and loser-take-all (LTA) circuits are studied, and their operations are analyzed in this review. The exclusive operation of the current conveyor, binary tree, and time-domain WTA/LTA architectures, as the most important architectures reported in the literature, are compared from the perspectives of power consumption, speed, and precision.

Full article

(This article belongs to the Special Issue State-of-the-Art in Integrated Circuit Design)

►▼

Show Figures

Figure 1

Open AccessArticle

A Survey of Automotive Radar and Lidar Signal Processing and Architectures

by

Luigi Giuffrida, Guido Masera and Maurizio Martina

Chips 2023, 2(4), 243-261; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2040015 - 08 Oct 2023

Abstract

►▼

Show Figures

In recent years, the development of Advanced Driver-Assistance Systems (ADASs) is driving the need for more reliable and precise on-vehicle sensing. Radar and lidar are crucial in this framework, since they allow sensing of vehicle’s surroundings. In such a scenario, it is necessary

[...] Read more.

In recent years, the development of Advanced Driver-Assistance Systems (ADASs) is driving the need for more reliable and precise on-vehicle sensing. Radar and lidar are crucial in this framework, since they allow sensing of vehicle’s surroundings. In such a scenario, it is necessary to master these sensing systems, and knowing their similarities and differences is important. Due to ADAS’s intrinsic real-time performance requirements, it is almost mandatory to be aware of the processing algorithms required by radar and lidar to understand what can be optimized and what actions can be taken to approach the real-time requirement. This review aims to present state-of-the-art radar and lidar technology, mainly focusing on modulation schemes and imaging systems, highlighting their weaknesses and strengths. Then, an overview of the sensor data processing algorithms is provided, with some considerations on what type of algorithms can be accelerated in hardware, pointing to some implementations from the literature. In conclusion, the basic concepts of sensor fusion are presented, and a comparison between radar and lidar is performed.

Full article

Figure 1

Open AccessFeature PaperArticle

Design and Performance Analysis of Hardware Realization of 3GPP Physical Layer for 5G Cell Search

by

Khalid Lodhi, Jayant Chhillar, Sumit J. Darak and Divisha Sharma

Chips 2023, 2(4), 223-242; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2040014 - 07 Oct 2023

Abstract

►▼

Show Figures

5G Cell Search (CS) is the first step for user equipment (UE) to initiate communication with the 5G node B (gNB) every time it is powered ON. In cellular networks, CS is accomplished via synchronization signals (SS) broadcasted by gNB. 5G 3rd generation

[...] Read more.

5G Cell Search (CS) is the first step for user equipment (UE) to initiate communication with the 5G node B (gNB) every time it is powered ON. In cellular networks, CS is accomplished via synchronization signals (SS) broadcasted by gNB. 5G 3rd generation partnership project (3GPP) specifications offer a detailed discussion on the SS generation at gNB, but a limited understanding of their blind search and detection is available. Unlike 4G, 5G SS may not be transmitted at the center of carrier frequency, and their frequency location is unknown to UE. In this work, we demonstrate the 5G CS by designing 3GPP compatible hardware realization of the physical layer (PHY) of the gNB transmitter and UE receiver. The proposed SS detection explores a novel down-sampling approach resulting in a 60% reduction in on-chip memory and 50% lower search time. Via detailed performance analysis, we analyze the functional correctness, computational complexity, and latency of the proposed approach for different word lengths, signal-to-noise ratio (SNR), and down-sampling factors. We demonstrate end-to-end 5G CS using GNU Radio-based RFNoC framework on the USRP-FPGA platform and achieve 66% faster SS search compared to software. The 3GPP compatibility and demonstration on hardware strengthen the commercial significance of the proposed work.

Full article

Figure 1

Open AccessTechnical Note

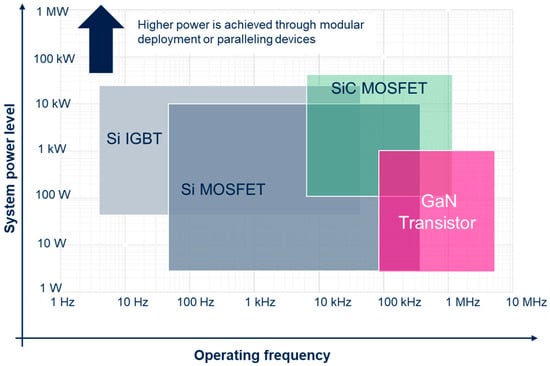

Silicon Carbide: Physics, Manufacturing, and Its Role in Large-Scale Vehicle Electrification

by

Filippo Di Giovanni

Chips 2023, 2(3), 209-222; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2030013 - 13 Sep 2023

Cited by 1

Abstract

►▼

Show Figures

Silicon carbide is changing power electronics; it is enabling massive car electrification owing to its far more efficient operation with respect to mainstream silicon in a large variety of energy conversion systems like the main traction inverter of an electric vehicle (EV). Its

[...] Read more.

Silicon carbide is changing power electronics; it is enabling massive car electrification owing to its far more efficient operation with respect to mainstream silicon in a large variety of energy conversion systems like the main traction inverter of an electric vehicle (EV). Its superior performance depends upon unique properties such as lower switching and conduction losses, safer high-temperature operation and high-voltage capability. Starting briefly with a description of its physics, more detailed information is then given about some key manufacturing steps such as crystal growth and epitaxy. Afterwards, an overview of its inherent defects and how to mitigate them is presented. Finally, a typical EV’s propulsion inverter is shown, proving the technology’s effectiveness in meeting requirements for mass electrification. Foreword: In recent years, SiC has drawn the attention of a growing number of power electronics designers as the material has good prospects for reducing environmental impacts on a global basis. The goal of this paper, based on the author’s contribution to the introduction of the technology at STMicroelectronics, is to show the potential of silicon carbide in enabling massive car electrification. The company’s SiC MOSFETs, tailored to the automotive industry, are enabling visionary EV makers to pave the way for sustainable e-mobility. The intent of this paper is to describe, for a large crowd of readers, how SiC features can accelerate such a transition by quantifying the benefits they bring in terms of improved efficiency in an EV electric powertrain. The paper also has the ambition to highlight the material’s physics and to give an overview of its production processes, starting from the crystal growth for realizing substrates to the main epitaxy techniques. Some space has been devoted to the analysis of the main crystal defects not present in silicon and whose nature poses new challenges in terms of manufacturing yields and screening. Finally, some insights into the market evolution and on the transition to 200 mm wafers are given.

Full article

Figure 1

Open AccessArticle

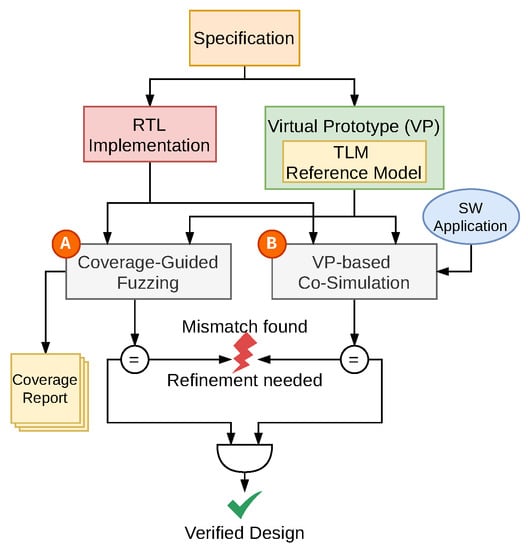

Synergistic Verification of Hardware Peripherals through Virtual Prototype Aided Cross-Level Methodology Leveraging Coverage-Guided Fuzzing and Co-Simulation

by

Sallar Ahmadi-Pour, Mathis Logemann, Vladimir Herdt and Rolf Drechsler

Chips 2023, 2(3), 195-208; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2030012 - 08 Sep 2023

Abstract

►▼

Show Figures

In this paper, we propose a Virtual Prototype (VP) driven verification methodology for Hardware (HW) peripherals. In particular, we combine two approaches that complement each other and use the VP as a readily available reference model: We use (A) Coverage-Guided Fuzzing (CGF) which

[...] Read more.

In this paper, we propose a Virtual Prototype (VP) driven verification methodology for Hardware (HW) peripherals. In particular, we combine two approaches that complement each other and use the VP as a readily available reference model: We use (A) Coverage-Guided Fuzzing (CGF) which enables comprehensive verification at the unit-level of the Register-Transfer Level (RTL) HW peripheral with a Transaction Level Modeling (TLM) reference, and (B) an application-driven co-simulation-based approach that enables verification of the HW peripheral at the system-level. As a case-study, we utilize a RISC-V Platform Level Interrupt Controller (PLIC) as HW peripheral and use an abstract TLM PLIC implementation from the open source RISC-V VP as the reference model. In our experiments we find three behavioral mismatches and discuss the observation of these, as well as non-functional timing behavior mismatches, that were found through the proposed synergistic approach. Furthermore, we provide a discussion and considerations on the RTL/TLM Transactors, as they embody one keystone in cross-level methods. As the different approaches uncover different mismatches in our case-study (e.g., behavioral mismatches and timing mismatches), we conclude a synergy between the methods to aid in verification efforts.

Full article

Figure 1

Open AccessArticle

Standard-Cell-Based Comparators for Ultra-Low Voltage Applications: Analysis and Comparisons

by

Riccardo Della Sala, Francesco Centurelli, Giuseppe Scotti and Gaetano Palumbo

Chips 2023, 2(3), 173-194; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2030011 - 18 Aug 2023

Cited by 2

Abstract

►▼

Show Figures

This work is focused on the performance of three different standard-cell-based comparator topologies, considering ultra-low-voltage (ULV) operation. The main application scenarios in which standard-cell-based comparators can be exploited are considered, and a set of figures of merit (FoM) to allow an in-depth comparison

[...] Read more.

This work is focused on the performance of three different standard-cell-based comparator topologies, considering ultra-low-voltage (ULV) operation. The main application scenarios in which standard-cell-based comparators can be exploited are considered, and a set of figures of merit (FoM) to allow an in-depth comparison among the different topologies is introduced. Then, a set of simulation testbenches are defined in order to simulate and compare the considered topologies implemented in both a 130 nm technology and a 28 nm FDSOI CMOS process. Propagation delay, power consumption and power–delay product are evaluated for different values of the input common mode voltage, as a function of input differential amplitude, and in different supply voltage and temperature conditions. Monte Carlo simulations to evaluate the input offset voltage under mismatch variations are also provided. Simulation results show that the performances of the different comparator topologies are strongly dependent on the input common mode voltage, and that the best values for all the performance figures of merit are achieved by the comparator based on three-input NAND gates, with the only limitation being its non-rail-to-rail input common mode range (ICMR). The performances of the considered comparator topologies have also been simulated for different values of the supply voltage, ranging from 0.3 V to 1.2 V, showing that, even if standard-cell-based comparators can be operated at higher supply voltages by scaling their performances accordingly, the best values of the FoMs are achieved for

Figure 1

Open AccessArticle

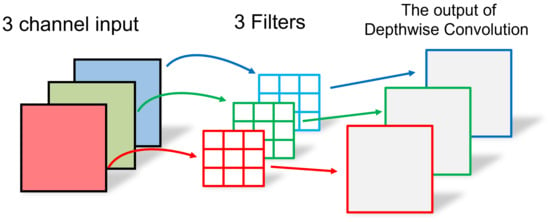

A-DSCNN: Depthwise Separable Convolutional Neural Network Inference Chip Design Using an Approximate Multiplier

by

Jin-Jia Shang, Nicholas Phipps, I-Chyn Wey and Tee Hui Teo

Chips 2023, 2(3), 159-172; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2030010 - 19 Jul 2023

Cited by 1

Abstract

►▼

Show Figures

For Convolutional Neural Networks (CNNs), Depthwise Separable CNN (DSCNN) is the preferred architecture for Application Specific Integrated Circuit (ASIC) implementation on edge devices. It benefits from a multi-mode approximate multiplier proposed in this work. The proposed approximate multiplier uses two 4-bit multiplication operations

[...] Read more.

For Convolutional Neural Networks (CNNs), Depthwise Separable CNN (DSCNN) is the preferred architecture for Application Specific Integrated Circuit (ASIC) implementation on edge devices. It benefits from a multi-mode approximate multiplier proposed in this work. The proposed approximate multiplier uses two 4-bit multiplication operations to implement a 12-bit multiplication operation by reusing the same multiplier array. With this approximate multiplier, sequential multiplication operations are pipelined in a modified DSCNN to fully utilize the Processing Element (PE) array in the convolutional layer. Two versions of Approximate-DSCNN (A-DSCNN) accelerators were implemented on TSMC 40 nm CMOS process with a supply voltage of 0.9 V. At a clock frequency of 200 MHz, the designs achieve 4.78 GOPs/mW and 4.89 GOP/mW power efficiency while occupying 1.16 mm

Figure 1

Open AccessArticle

On-Chip Adaptive Implementation of Neuromorphic Spiking Sensory Systems with Self-X Capabilities

by

Hamam Abd and Andreas König

Chips 2023, 2(2), 142-158; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2020009 - 06 Jun 2023

Abstract

►▼

Show Figures

In contemporary devices, the number and diversity of sensors is increasing, thus, requiring both efficient and robust interfacing to the sensors. Implementing the interfacing systems in advanced integration technologies faces numerous issues due to manufacturing deviations, signal swings, noise, etc. The interface sensor

[...] Read more.

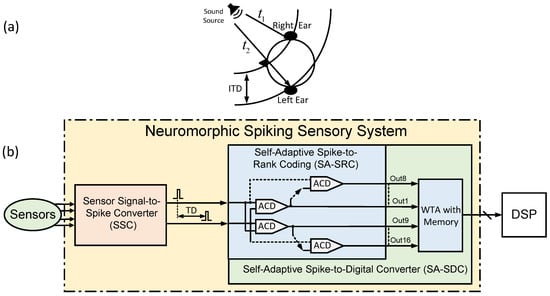

In contemporary devices, the number and diversity of sensors is increasing, thus, requiring both efficient and robust interfacing to the sensors. Implementing the interfacing systems in advanced integration technologies faces numerous issues due to manufacturing deviations, signal swings, noise, etc. The interface sensor designers escape to the time domain and digital design techniques to handle these challenges. Biology gives examples of efficient machines that have vastly outperformed conventional technology. This work pursues a neuromorphic spiking sensory system design with the same efficient style as biology. Our chip, that comprises the essential elements of the adaptive neuromorphic spiking sensory system, such as the neuron, synapse, adaptive coincidence detection (ACD), and self-adaptive spike-to-rank coding (SA-SRC), was manufactured in XFAB CMOS 0.35

Figure 1

Open AccessArticle

A Quantitative Review of Automated Neural Search and On-Device Learning for Tiny Devices

by

Danilo Pietro Pau, Prem Kumar Ambrose and Fabrizio Maria Aymone

Chips 2023, 2(2), 130-141; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2020008 - 09 May 2023

Cited by 5

Abstract

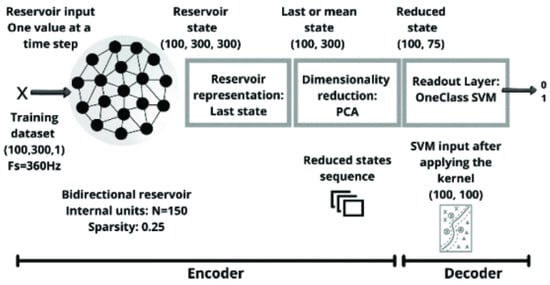

This paper presents a state-of-the-art review of different approaches for Neural Architecture Search targeting resource-constrained devices such as microcontrollers, as well as the implementations of on-device learning techniques for them. Approaches such as MCUNet have been able to drive the design of tiny

[...] Read more.

This paper presents a state-of-the-art review of different approaches for Neural Architecture Search targeting resource-constrained devices such as microcontrollers, as well as the implementations of on-device learning techniques for them. Approaches such as MCUNet have been able to drive the design of tiny neural architectures with low memory and computational requirements which can be deployed effectively on microcontrollers. Regarding on-device learning, there are various solutions that have addressed concept drift and have coped with the accuracy drop in real-time data depending on the task targeted, and these rely on a variety of learning methods. For computer vision, MCUNetV3 uses backpropagation and represents a state-of-the-art solution. The Restricted Coulomb Energy Neural Network is a promising method for learning with an extremely low memory footprint and computational complexity, which should be considered for future investigations.

Full article

(This article belongs to the Topic Artificial Intelligence in Smart Industrial Diagnostics and Manufacturing)

►▼

Show Figures

Figure 1

Open AccessArticle

Low-Cost Indirect Measurements for Power-Efficient In-Field Optimization of Configurable Analog Front-Ends with Self-X Properties: A Hardware Implementation

by

Qummar Zaman, Senan Alraho and Andreas König

Chips 2023, 2(2), 102-129; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2020007 - 01 May 2023

Cited by 1

Abstract

►▼

Show Figures

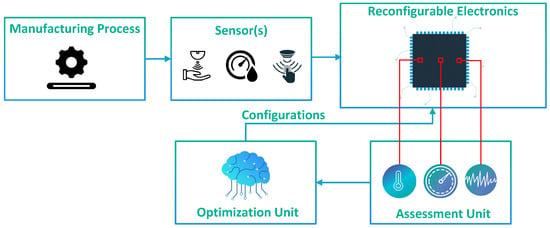

This paper presents a practical implementation and measurement results of power-efficient chip performance optimization, utilizing low-cost indirect measurement methods to support self-X properties (self-calibration, self-healing, self-optimization, etc.) for in-field optimization of analog front-end sensory electronics with XFAB 0.35 µm complementary metal oxide semiconductor

[...] Read more.

This paper presents a practical implementation and measurement results of power-efficient chip performance optimization, utilizing low-cost indirect measurement methods to support self-X properties (self-calibration, self-healing, self-optimization, etc.) for in-field optimization of analog front-end sensory electronics with XFAB 0.35 µm complementary metal oxide semiconductor (CMOS) technology. The reconfigurable, fully differential indirect current-feedback instrumentation amplifier (CFIA) performance is intrinsically optimized by employing a single test sinusoidal signal stimulus and measuring the total harmonic distortion (THD) at the output. To enhance the optimization process, the experience replay particle swarm optimization (ERPSO) algorithm is utilized as an artificial intelligence (AI) agent, implemented at the hardware level, to optimize the performance characteristics of the CFIA. The ERPSO algorithm extends the selection producer capabilities of the classical PSO methodology by incorporating an experience replay buffer to mitigate the likelihood of being trapped in local optima. Furthermore, the CFIA circuit has been integrated with a simple power-monitoring module to assess the power consumption of the optimization solution, to achieve a power-efficient and reliable configuration. The optimized chip performance showed an approximate 34% increase in power efficiency while achieving a targeted THD value of −72 dB, utilizing a 1 Vp-p differential input signal with a frequency of 1 MHz, and consuming approximately 53 mW of power. Preliminary tests conducted on the fabricated chip, using the default configuration pattern extrapolated from post-layout simulations, revealed an unacceptable performance behavior of the CFIA. Nevertheless, the proposed in-field optimization successfully restored the circuit’s performance, resulting in a robust design that meets the performance achieved in the design phase.

Full article

Figure 1

Open AccessReview

Silicon Radiation Detector Technologies: From Planar to 3D

by

Gian-Franco Dalla Betta and Jixing Ye

Chips 2023, 2(2), 83-101; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2020006 - 13 Apr 2023

Cited by 7

Abstract

Silicon radiation detectors, a special type of microelectronic sensor which plays a crucial role in many applications, are reviewed in this paper, focusing on fabrication aspects. After addressing the basic concepts and the main requirements, the evolution of detector technologies is discussed, which

[...] Read more.

Silicon radiation detectors, a special type of microelectronic sensor which plays a crucial role in many applications, are reviewed in this paper, focusing on fabrication aspects. After addressing the basic concepts and the main requirements, the evolution of detector technologies is discussed, which has been mainly driven by the ever-increasing demands for frontier scientific experiments.

Full article

(This article belongs to the Special Issue Smart IC Design and Sensing Technologies)

►▼

Show Figures

Figure 1

Open AccessReview

Approximate Content-Addressable Memories: A Review

by

Esteban Garzón, Leonid Yavits, Adam Teman and Marco Lanuzza

Chips 2023, 2(2), 70-82; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2020005 - 30 Mar 2023

Cited by 3

Abstract

►▼

Show Figures

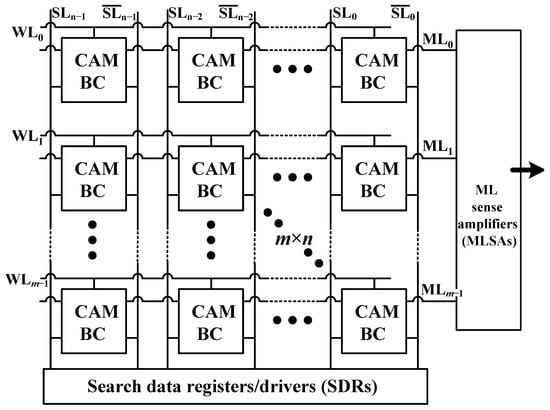

Content-addressable memory (CAM) has been part of the memory market for more than five decades. CAM can carry out a single clock cycle lookup based on the content rather than an address. Thanks to this attractive feature, CAM is utilized in memory systems

[...] Read more.

Content-addressable memory (CAM) has been part of the memory market for more than five decades. CAM can carry out a single clock cycle lookup based on the content rather than an address. Thanks to this attractive feature, CAM is utilized in memory systems where a high-speed content lookup technique is required. However, typical CAM applications only support exact matching, as opposed to approximate matching, where a certain Hamming distance (several mismatching characters between a query pattern and the dataset stored in CAM) needs to be tolerated. Recent interest in approximate search has led to the development of new CAM-based alternatives, accelerating the processing of large data workloads in the realm of big data, genomics, and other data-intensive applications. In this review, we provide an overview of approximate CAM and describe its current and potential applications that would benefit from approximate search computing.

Full article

Figure 1

Open AccessReview

Bandpass Sigma–Delta Modulation: The Path toward RF-to-Digital Conversion in Software-Defined Radio

by

Jose M. de la Rosa

Chips 2023, 2(1), 44-69; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2010004 - 02 Mar 2023

Abstract

►▼

Show Figures

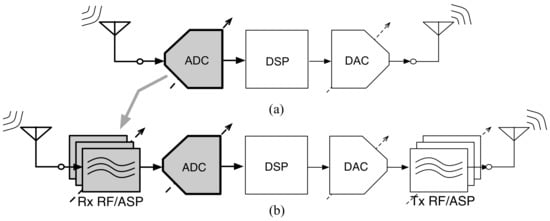

This paper reviews the state of the art on bandpass

This paper reviews the state of the art on bandpass

Figure 1

Open AccessArticle

Methodology for a Low-Power and Low-Circuit-Area 15-Bit SAR ADC Using Split-Capacitor Mismatch Compensation and a Dynamic Element Matching Algorithm

by

William Bontems and Daniel Dzahini

Chips 2023, 2(1), 31-43; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2010003 - 27 Feb 2023

Abstract

►▼

Show Figures

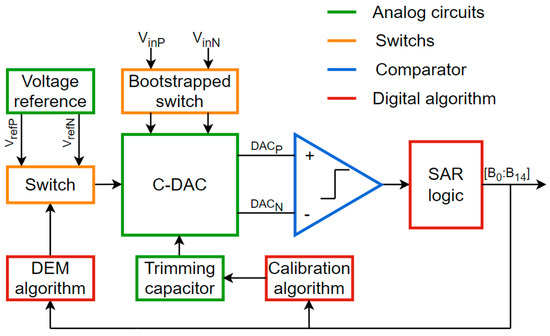

This paper presents a design methodology for a low-power, low-chip-area, and high-resolution successive approximations register (SAR) analog-to-digital converter (ADC). The proposed method includes a segmented capacitive DAC (C-DAC) to reduce the power consumption and the total area. An embedded self-calibration algorithm based on

[...] Read more.

This paper presents a design methodology for a low-power, low-chip-area, and high-resolution successive approximations register (SAR) analog-to-digital converter (ADC). The proposed method includes a segmented capacitive DAC (C-DAC) to reduce the power consumption and the total area. An embedded self-calibration algorithm based on a set of trimming capacitors was applied alongside a dynamic element matching (DEM) procedure to control the inherent linearity issues caused by the process mismatch. The SAR ADC and each additional algorithm were modeled in MATLAB to show their efficiency. Finally, a simple methodology was developed to allow for the fast estimation of signal-to-noise ratios (SNRs) without any FFT calculation.

Full article

Figure 1

Open AccessArticle

An Interface Platform for Robotic Neuromorphic Systems

by

Nicola Russo, Haochun Huang, Eugenio Donati, Thomas Madsen and Konstantin Nikolic

Chips 2023, 2(1), 20-30; https://0-doi-org.brum.beds.ac.uk/10.3390/chips2010002 - 01 Feb 2023

Cited by 1

Abstract

►▼

Show Figures

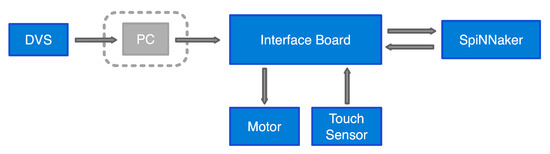

Neuromorphic computing is promising to become a future standard in low-power AI applications. The integration between new neuromorphic hardware and traditional microcontrollers is an open challenge. In this paper, we present an interface board and a communication protocol that allows communication between different

[...] Read more.

Neuromorphic computing is promising to become a future standard in low-power AI applications. The integration between new neuromorphic hardware and traditional microcontrollers is an open challenge. In this paper, we present an interface board and a communication protocol that allows communication between different devices, using a microcontroller unit (Arduino Due) in the middle. Our compact printed circuit board (PCB) links different devices as a whole system and provides a power supply for the entire system using batteries as the power supply. Concretely, we have connected a Dynamic Vision Sensor (DVS128), SpiNNaker board and a servo motor, creating a platform for a neuromorphic robotic system controlled by a Spiking Neural Network, which is demonstrated on the task of intercepting incoming objects. The data rate of the implemented interface board is 24.64 k symbols/s and the latency for generating commands is about 11ms. The complete system is run only by batteries, making it very suitable for robotic applications.

Full article

Figure 1

Highly Accessed Articles

Latest Books

E-Mail Alert

News

Topics

Topic in

Applied Sciences, Electronics, Materials, Applied Nano, Technologies, Inventions, Chips

Advances in Microelectronics and Semiconductor Engineering

Topic Editors: Gerard Ghibaudo, Francis BalestraDeadline: 30 September 2024

Topic in

Applied Sciences, Batteries, Electricity, Electronics, Sensors, WEVJ, Technologies, Chips

Advanced Wireless Charging Technology

Topic Editors: Chong Zhu, Kailong LiuDeadline: 31 October 2024

Topic in

Electronics, Applied Sciences, BDCC, Mathematics, Chips

Theory and Applications of High Performance Computing

Topic Editors: Pavel Lyakhov, Maxim DeryabinDeadline: 30 November 2024

Topic in

Applied Sciences, Electronics, Entropy, Mathematics, Symmetry, Technologies, Chips

Quantum Information and Quantum Computing, 2nd Volume

Topic Editors: Durdu Guney, David PetrosyanDeadline: 31 March 2025

Conferences

Special Issues

Special Issue in

Chips

New Advances in Memristors: Design and Applications

Guest Editor: Arindam BalaDeadline: 31 December 2024