Efficient and Accurate Analog Voltage Measurement Using a Direct Sensor-to-Digital Port Interface for Microcontrollers and Field-Programmable Gate Arrays

Abstract

:1. Introduction

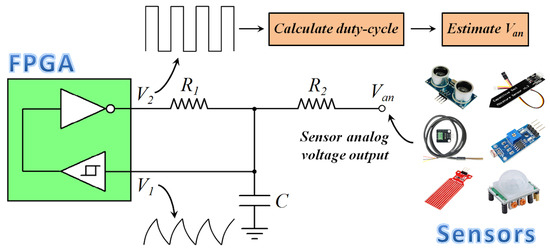

2. Measurement Technique

2.1. Working Principle

2.2. Digital Interface Parameters in Commercial Devices

2.3. Circuits to Change the Digital Interface Parameters

3. Circuit Simulations

3.1. Digital Interface with Vt = 1.65 V and ΔV = 0.5 V

3.2. Digital Interface with Vt = 1.65 V and ΔV Variable

3.3. Digital Interface with Vt Variable and ΔV = 0.5 V

3.4. Maximum Performance of the Proposed Method

4. Implementation in a FPGA Device

- (1)

- An 8 bit command is sent from the PC to the FPGA using UART to request the value of the duty cycle of signal V2.

- (2)

- The FPGA module ‘count periods’ calculates the length of time signal V2 is high (tH) and low (tL) and stores these data in two 16 bit registers.

- (3)

- The FPGA module ‘division calculation’ calculates the duty cycle of signal V2 from the 16 bit registers thigh and tlow and stores the result in the 32 bit register division_result.

- (4)

- The measured duty cycle is sent from the FPGA to the PC using UART with four 8 bit data transfers.

5. Experimental Results

6. Comparison with the State of the Art

7. Conclusions

Supplementary Materials

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Pistoia, G. Battery Operated Devices and Systems: From Portable Electronics to Industrial Products; Elsevier: Amsterdam, The Netherlands, 2008. [Google Scholar]

- Grossi, M. Energy harvesting strategies for wireless sensor networks and mobile devices: A review. Electronics 2021, 10, 661. [Google Scholar] [CrossRef]

- Sgobba, F.; Sampaolo, A.; Patimisco, P.; Giglio, M.; Menduni, G.; Ranieri, A.C.; Hoelzl, C.; Rossmadl, H.; Brehm, C.; Mackowiak, V.; et al. Compact and portable quartz-enhanced photoacoustic spectroscopy sensor for carbon monoxide environmental monitoring in urban areas. Photoacoustics 2022, 25, 100318. [Google Scholar] [CrossRef]

- Salamone, F.; Masullo, M.; Sibilio, S. Wearable devices for environmental monitoring in the built environment: A systematic review. Sensors 2021, 21, 4727. [Google Scholar] [CrossRef]

- Singh, G.; Kim, S.; Lee, K. Development of a highly sensitive and portable particulate matter SAW sensor and interface electronics. Sens. Actuators A Phys. 2022, 343, 113641. [Google Scholar] [CrossRef]

- Grossi, M.; Valli, E.; Bendini, A.; Gallina Toschi, T.; Riccò, B. A Portable Battery-Operated Sensor System for Simple and Rapid Assessment of Virgin Olive Oil Quality Grade. Chemosensors 2022, 10, 102. [Google Scholar] [CrossRef]

- Grossi, M.; Bendini, A.; Valli, E.; Gallina Toschi, T. Field-Deployable Determinations of Peroxide Index and Total Phenolic Content in Olive Oil Using a Promising Portable Sensor System. Sensors 2023, 23, 5002. [Google Scholar] [CrossRef] [PubMed]

- Ghatak, B.; Banerjee, S.; Ali, S.B.; Das, N.; Tudu, B.; Pramanik, P.; Mukherji, S.; Bandyopadhyay, R. Development of a low-cost portable aroma sensing system for identifying artificially ripened mango. Sens. Actuators A Phys. 2021, 331, 112964. [Google Scholar] [CrossRef]

- Daou, B.; Elbadi, M.; Alkaisi, A.; Elwakil, A.S. Body Mass Composition Measurements Using a Portable Device. In Proceedings of the IEEE 4th Novel Intelligent and Leading Emerging Sciences Conference (NILE), Giza, Egypt, 22–24 October 2022; pp. 159–162. [Google Scholar]

- Muñoz, J.D.; Mosquera, V.H.; Rengifo, C.F. A low-cost, portable, two-dimensional bioimpedance distribution estimation system based on the AD5933 impedance converter. HardwareX 2022, 11, e00274. [Google Scholar] [CrossRef] [PubMed]

- Choi, A.; Kim, J.Y.; Jo, S.; Jee, J.H.; Heymsfield, S.B.; Bhagat, Y.A.; Kim, I.; Cho, J. Smartphone-Based Bioelectrical Impedance Analysis Devices for Daily Obesity Management. Sensors 2015, 15, 22151–22166. [Google Scholar] [CrossRef]

- Grossi, M.; Parolin, C.; Vitali, B.; Riccò, B. Computer Vision Approach for the Determination of Microbial Concentration and Growth Kinetics Using a Low Cost Sensor System. Sensors 2019, 19, 5367. [Google Scholar] [CrossRef] [PubMed]

- Salmeron, J.F.; Vela-Cano, M.; Falco, A.; Rivadeneyra, M.A.; Becherer, M.; Lugli, P.; Gonzalez-Lopez, J.; Rivadeneyra, A. Portable electronic system for fast detection of bacteria lactase fermentation in water samples. Sens. Actuators A Phys. 2022, 338, 113486. [Google Scholar] [CrossRef]

- Grossi, M.; Parolin, C.; Vitali, B.; Riccò, B. Measurement of bacterial concentration using a portable sensor system with a combined electrical-optical approach. IEEE Sens. J. 2019, 19, 10693–10700. [Google Scholar] [CrossRef]

- Meléndez, F.; Arroyo, P.; Gómez-Suárez, J.; Palomeque-Mangut, S.; Suárez, J.I.; Lozano, J. Portable electronic nose based on digital and analog chemical sensors for 2, 4, 6-trichloroanisole discrimination. Sensors 2022, 22, 3453. [Google Scholar] [CrossRef] [PubMed]

- Shi, L.; Tang, Q.; Yang, B.; Liu, W.; Li, B.; Yang, C.; Jin, Y. Portable and Label-Free Sensor Array for Discriminating Multiple Analytes via a Handheld Gas Pressure Meter. Anal. Chem. 2022, 94, 14453–14459. [Google Scholar] [CrossRef] [PubMed]

- Grossi, M.; Riccò, B. A portable electronic system for in-situ measurements of oil concentration in MetalWorking fluids. Sens. Actuators A Phys. 2016, 243, 7–14. [Google Scholar] [CrossRef]

- Sridhar, S.; Sankar, K.R.; Sreeshylam, P.; Parivallal, S.; Kesavan, K.; Murthy, S.G.N. Remote structural health monitoring of civil infrastructures-recent trends. Int. J. Comadem 2008, 11, 25. [Google Scholar]

- Martín, C.; Garrido, D.; Llopis, L.; Rubio, B.; Díaz, M. Facilitating the monitoring and management of structural health in civil infrastructures with an Edge/Fog/Cloud architecture. Comput. Stand. Interfaces 2022, 81, 103600. [Google Scholar] [CrossRef]

- Gopalakrishnan, K.; Ceylan, H.; Kim, S.; Yang, S. Wireless MEMS for Transportation Infrastructure Health Monitoring. In Wireless MEMS Networks and Applications; Woodhead Publishing: Sawston, UK, 2017; pp. 53–76. [Google Scholar]

- Xie, S.; Wang, Y. A Data Weight Averaging-Inspired Digital Calibration Method for a 10-Bit Noise-Shaping Successive Approximation Register. Electronics 2023, 12, 3046. [Google Scholar] [CrossRef]

- Chen, T.; Park, C.; Chaganti, S.K.; Silva-Martinez, J.; Geiger, R.L.; Chen, D. An ultrafast multibit/stage pipelined ADC testing and calibration method. IEEE Trans. Instrum. Meas. 2019, 69, 729–738. [Google Scholar] [CrossRef]

- Li, T.; Zhang, Y.; Ni, Y. An Ultra-fast ADC Linearity Test and Calibration Method. In Proceedings of the IEEE 13th International Conference on Anti-Counterfeiting, Security, and Identification (ASID), Xiamen, China, 25–27 October 2019; pp. 282–285. [Google Scholar]

- Juan, Y.H.; Huang, H.Y.; Lee, S.Y.; Lai, S.C.; Juang, W.H.; Luo, C.H. A self-testing platform with a foreground digital calibration technique for SAR ADCs. Appl. Sci. 2016, 6, 217. [Google Scholar] [CrossRef]

- Hernández-Gutiérrez, C.A.; Delgado-del-Carpio, M.; Zebadúa-Chavarría, L.A.; Hernández-de-León, H.R.; Escobar-Gómez, E.N.; Quevedo-López, M. IoT-Enabled System for Detection, Monitoring, and Tracking of Nuclear Materials. Electronics 2023, 12, 3042. [Google Scholar] [CrossRef]

- Samadpoor Rikan, B.; Kim, S.Y.; Ahmad, N.; Abbasizadeh, H.; Riaz Ur Rehman, M.; Shehzad, K.; Hejazi, A.; Rad, R.E.; Verma, D.; Lee, K.Y. A sigma-delta ADC for signal conditioning IC of automotive piezo-resistive pressure sensors with over 80 dB SNR. Sensors 2018, 18, 4199. [Google Scholar] [CrossRef] [PubMed]

- Reverter, F. A microcontroller-based interface circuit for non-linear resistive sensors. Meas. Sci. Technol. 2020, 32, 027001. [Google Scholar] [CrossRef]

- Reverter, F. A microcontroller-based interface circuit for three-wire connected resistive sensors. IEEE Trans. Instrum. Meas. 2022, 71, 1–4. [Google Scholar] [CrossRef]

- Reverter, F. A direct approach for interfacing four-wire resistive sensors to microcontrollers. Meas. Sci. Technol. 2022, 34, 037001. [Google Scholar] [CrossRef]

- Areekath, L.; George, B.; Reverter, F. Analysis of a direct microcontroller interface for capacitively coupled resistive sensors. IEEE Trans. Instrum. Meas. 2020, 70, 1–10. [Google Scholar] [CrossRef]

- Czaja, Z. A measurement method for capacitive sensors based on a versatile direct sensor-to-microcontroller interface circuit. Measurement 2020, 155, 107547. [Google Scholar] [CrossRef]

- Czaja, Z. A measurement method for lossy capacitive relative humidity sensors based on a direct sensor-to-microcontroller interface circuit. Measurement 2021, 170, 108702. [Google Scholar] [CrossRef]

- Hidalgo-Lopez, J.A.; Castellanos-Ramos, J. Simplifying capacitive sensor readout using a new direct interface circuit. IEEE Trans. Instrum. Meas. 2022, 72, 2000910. [Google Scholar] [CrossRef]

- Kokolanski, Z.; Jordana, J.; Gasulla, M.; Dimcev, V.; Reverter, F. Direct inductive sensor-to-microcontroller interface circuit. Sens. Actuators A Phys. 2015, 224, 185–191. [Google Scholar] [CrossRef]

- Kokolanski, Z.; Gasulla, M.; Reverter, F. Differential Inductive Sensor-to-Microcontroller Interface Circuit. In Proceedings of the IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Auckland, New Zealand, 20–23 May 2019; pp. 1–5. [Google Scholar]

- Asif, A.; Ali, A.; Abdin, M.Z.U. Resolution enhancement in directly interfaced system for inductive sensors. IEEE Trans. Instrum. Meas. 2018, 68, 4104–4111. [Google Scholar] [CrossRef]

- Peter, D.; Baker, B.C.; Butler, D.; Darmawaskita, H. Make a Delta-Sigma Converter Using a Microcontroller’s Analog Comparator Module; Microchip Technology Inc.: Chandler, AZ, USA, 1998. [Google Scholar]

- Soldera, J.D.B.; Espindola, M.; Olmos, A. Implementing a 10-Bit Sigma-Delta Analog-to-Digital Converter Using the HC9S08Rx MCU Family Analog Comparator. Free. Semicond. 2005, 1–22. Available online: https://www.nxp.com/docs/en/application-note/AN2688.pdf (accessed on 20 November 2023).

- Weber, P.; Windish, C. Build a complete industrial-ADC interface using a microcontroller and a sigma-delta modulator. EDN 2007, 52, 63. [Google Scholar]

- Integrated ADC for Altera Cyclone-IV Devices, Missing Link Electronics, Technical Brief. 2011. Available online: https://www.missinglinkelectronics.com/wp-content/uploads/2012/08/MLE-TB20110419.pdf (accessed on 20 November 2023).

- Bengtsson, L. Direct analog-to-microcontroller interfacing. Sens. Actuators A Phys. 2012, 179, 105–113. [Google Scholar] [CrossRef]

- Raspberry Pi Pico Development Board. Available online: https://www.raspberrypi.com/products/raspberry-pi-pico/ (accessed on 20 November 2023).

- Nucleo L073RZ Development Board. Available online: https://www.st.com/en/evaluation-tools/nucleo-l073rz.html (accessed on 20 November 2023).

- Arduino Due Development Board. Available online: https://docs.arduino.cc/hardware/due (accessed on 20 November 2023).

- Basys 3 Artix-7 FPGA Development Board. Available online: https://digilent.com/shop/basys-3-artix-7-fpga-trainer-board-recommended-for-introductory-users/ (accessed on 20 November 2023).

- Zybo Zync-7000 FPGA Development Board. Available online: https://digilent.com/reference/programmable-logic/zybo/start (accessed on 20 November 2023).

- Tang Nano 9k FPGA Development Board. Available online: https://wiki.sipeed.com/hardware/en/tang/Tang-Nano-9K/Nano-9K.html (accessed on 20 November 2023).

- LTSpice Circuit Simulator. Available online: https://www.analog.com/en/design-center/design-tools-and-calculators/ltspice-simulator.html (accessed on 4 January 2024).

- Icarus Verilog Simulator. Available online: https://bleyer.org/icarus/ (accessed on 20 November 2023).

- Verilog Implementation of the Circuit for Binary Division. Available online: https://projectf.io/posts/division-in-verilog/ (accessed on 20 November 2023).

- Gowin GW1NR Series Data Sheet. Available online: https://cdn.gowinsemi.com.cn/DS117E.pdf (accessed on 4 January 2024).

- Reference Design: Simple Sigma-Delta ADC, FPGA-RD-02047-1.6, Lattice Semiconductor. Available online: https://www.latticesemi.com/products/designsoftwareandip/intellectualproperty/referencedesigns/referencedesign03/simplesigmadeltaadc (accessed on 6 January 2024).

| Device | Device Type | Development Board | Ref. | VH (V) | VL (V) | Vt (V) | ΔV (mV) | CVΔV |

|---|---|---|---|---|---|---|---|---|

| STM32L073RZT6 | microcontroller | Nucleo-L073RZ | [43] | 1.644 | 1.196 | 1.420 | 448 | 1.827 |

| Atmel SAM3X8E | microcontroller | Arduino Due | [44] | 1.481 | 1.272 | 1.376 | 209 | 4.877 |

| XC7A35T-1CPG236C | FPGA | Basys 3 | [45] | 1.281 | 1.228 | 1.254 | 52 | 6.527 |

| XC7Z010-1CLG400C | FPGA | Zybo | [46] | 1.337 | 1.239 | 1.288 | 97 | 1.425 |

| Gowin GW1NR-9 | FPGA | Tang Nano 9k | [47] | 1.753 | 1.387 | 1.570 | 367 | 1.558 |

| R2 (kΩ) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 120 | 62 | 35 | 27 | 22 | 18 | 17 | 16 | 15 | 14 | |

| C = 320 nF | 2.21 | 1.12 | 0.59 | 0.42 | 0.31 | 0.22 | 0.19 | 0.17 | 0.14 | 0.10 |

| C = 150 nF | 4.71 | 2.36 | 1.25 | 0.90 | 0.67 | 0.47 | 0.41 | 0.35 | 0.29 | 0.22 |

| C = 60 nF | 11.77 | 5.91 | 3.13 | 2.25 | 1.67 | 1.17 | 1.03 | 0.89 | 0.73 | 0.55 |

| C = 47 nF | 15.03 | 7.54 | 3.99 | 2.88 | 2.14 | 1.49 | 1.32 | 1.13 | 0.93 | 0.70 |

| C = 32 nF | 22.09 | 11.01 | 5.86 | 4.23 | 3.14 | 2.19 | 1.93 | 1.66 | 1.37 | 1.03 |

| C = 20 nF | 35.31 | 17.72 | 9.38 | 6.76 | 5.02 | 3.51 | 3.09 | 2.66 | 2.19 | 1.64 |

| C = 14 nF | 50.44 | 25.32 | 13.40 | 9.66 | 7.18 | 5.01 | 4.42 | 3.80 | 3.12 | 2.35 |

| C = 9 nF | 78.47 | 39.39 | 20.85 | 15.03 | 11.17 | 7.79 | 6.88 | 5.91 | 4.86 | 3.66 |

| C = 5 nF | 141.25 | 70.89 | 37.53 | 27.06 | 20.10 | 14.03 | 12.38 | 10.63 | 8.74 | 6.58 |

| C = 2 nF | 353.12 | 177.24 | 93.83 | 67.65 | 50.26 | 35.07 | 30.94 | 26.58 | 21.86 | 16.46 |

| C = 1 nF | 706.30 | 354.53 | 187.67 | 135.30 | 100.52 | 70.15 | 61.89 | 53.12 | 43.72 | 32.92 |

| R2 (kΩ) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 120 | 62 | 35 | 27 | 22 | 18 | 17 | 16 | 15 | 14 | |

| C = 320 nF | 510 | 497 | 469 | 441 | 404 | 349 | 327 | 300 | 266 | 218 |

| C = 150 nF | 1089 | 1062 | 1002 | 941 | 863 | 744 | 698 | 641 | 568 | 465 |

| C = 60 nF | 2724 | 2655 | 2505 | 2353 | 2159 | 1861 | 1747 | 1604 | 1420 | 1163 |

| C = 47 nF | 3478 | 3389 | 3197 | 3004 | 2757 | 2376 | 2230 | 2048 | 1812 | 1485 |

| C = 32 nF | 5113 | 4978 | 4696 | 4412 | 4049 | 3491 | 3275 | 3008 | 2662 | 2182 |

| C = 20 nF | 8174 | 7965 | 7515 | 7060 | 6479 | 5585 | 5241 | 4813 | 4260 | 3491 |

| C = 14 nF | 11,678 | 11,379 | 10,736 | 10,086 | 9256 | 7979 | 7487 | 6875 | 6086 | 4988 |

| C = 9 nF | 18,165 | 17,701 | 16,700 | 15,690 | 14,398 | 12,412 | 11,647 | 10,695 | 9467 | 7759 |

| C = 5 nF | 32,698 | 31,862 | 30,060 | 28,242 | 25,916 | 22,342 | 20,964 | 19,252 | 17,042 | 13,967 |

| C = 2 nF | 81,746 | 79,655 | 75,154 | 70,606 | 64,792 | 55,856 | 52,413 | 48,132 | 42,605 | 34,919 |

| C = 1 nF | 163,505 | 159,337 | 150,308 | 141,203 | 129,584 | 111,719 | 104,832 | 96,190 | 85,207 | 69,842 |

| R2 (kΩ) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 120 | 62 | 35 | 27 | 22 | 18 | 17 | 16 | 15 | 14 | |

| C = 320 nF | 2.25 | 1.33 | 1.55 | 2.44 | 4.21 | 8.53 | 10.85 | 14.33 | 19.99 | 29.45 |

| C = 150 nF | 4.75 | 2.58 | 2.21 | 2.92 | 4.57 | 8.78 | 11.07 | 14.51 | 20.14 | 29.57 |

| C = 60 nF | 11.81 | 6.13 | 4.09 | 4.27 | 5.57 | 9.48 | 11.69 | 15.05 | 20.58 | 29.90 |

| C = 47 nF | 15.07 | 7.76 | 4.95 | 4.90 | 6.04 | 9.80 | 11.98 | 15.29 | 20.78 | 30.05 |

| C = 32 nF | 22.13 | 11.30 | 6.82 | 6.25 | 7.04 | 10.50 | 12.59 | 15.82 | 21.22 | 30.38 |

| C = 20 nF | 35.35 | 17.94 | 10.34 | 8.78 | 8.92 | 11.81 | 13.75 | 16.82 | 22.04 | 30.99 |

| C = 14 nF | 50.49 | 25.54 | 14.36 | 11.68 | 11.08 | 13.32 | 15.08 | 17.96 | 22.97 | 31.70 |

| C = 9 nF | 78.51 | 39.61 | 21.81 | 17.05 | 15.07 | 16.10 | 17.54 | 20.07 | 24.71 | 33.00 |

| C = 5 nF | 141.29 | 71.11 | 38.49 | 29.08 | 24.00 | 22.34 | 23.04 | 24.79 | 28.59 | 35.93 |

| C = 2 nF | 353.16 | 177.46 | 94.79 | 69.67 | 54.16 | 43.38 | 41.60 | 40.74 | 41.71 | 45.81 |

| C = 1 nF | 706.34 | 354.75 | 188.63 | 137.32 | 104.42 | 78.46 | 72.55 | 67.28 | 63.57 | 62.27 |

| R2 (kΩ) | |ΔVan| (mV) | σ (mV) | N | SRmax (Hz) |

|---|---|---|---|---|

| 15 | 14.57 | 16.18 | 20 | 7679.37 |

| 16.3 | 7.44 | 18.06 | 94 | 1680.08 |

| 18 | 5.69 | 19.82 | 194 | 847.50 |

| 22 | 2.68 | 24.64 | 1352 | 128.31 |

| 27 | 1.61 | 30.37 | 5708 | 31.35 |

| 32 | 1.09 | 37.22 | 18,665 | 9.75 |

| 38.8 | 1.18 | 43.97 | 22,074 | 8.36 |

| 47 | 1.46 | 53.42 | 21,510 | 8.66 |

| 67.8 | 2.19 | 77.13 | 19,901 | 9.45 |

| 81.7 | 2.63 | 93.02 | 20,064 | 9.40 |

| ADC Used | Device Type | Comparator Used | Measurement Range | Maximum Error | Maximum Sample Rate | LUT Used | Ref. |

|---|---|---|---|---|---|---|---|

| Yes | μcontroller | No | 0–3.3 V | 0.81 mV | 1 MHz | No | [43] |

| No | μcontroller | Yes | 0–5 V | 19.53 mV | 48.83 Hz | No | [37] |

| No | μcontroller | Yes | 0–3.3 V | 3.22 mV | 125 Hz | No | [38] |

| No | μcontroller | Yes | 0–10 V | − | − | No | [39] |

| No | FPGA | Yes | 0–3.3 V | 3.22 mV | 500 kHz | No | [40] |

| No | FPGA | Yes | 0–3.3 V | 12.88 mV | 7.63 kHz | No | [52] |

| No | μcontroller | No | 0–5 V | 1.22 mV | 65 Hz | Yes | [41] |

| No | FPGA | No | 0–3.3 V | 1.33 mV | 497 Hz | No | This work |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Grossi, M. Efficient and Accurate Analog Voltage Measurement Using a Direct Sensor-to-Digital Port Interface for Microcontrollers and Field-Programmable Gate Arrays. Sensors 2024, 24, 873. https://0-doi-org.brum.beds.ac.uk/10.3390/s24030873

Grossi M. Efficient and Accurate Analog Voltage Measurement Using a Direct Sensor-to-Digital Port Interface for Microcontrollers and Field-Programmable Gate Arrays. Sensors. 2024; 24(3):873. https://0-doi-org.brum.beds.ac.uk/10.3390/s24030873

Chicago/Turabian StyleGrossi, Marco. 2024. "Efficient and Accurate Analog Voltage Measurement Using a Direct Sensor-to-Digital Port Interface for Microcontrollers and Field-Programmable Gate Arrays" Sensors 24, no. 3: 873. https://0-doi-org.brum.beds.ac.uk/10.3390/s24030873